Linux rapidio- rio_test_dma 调试代码分析(3)

当前使用的驱动源码来自,驱动源码中包含block DMA的测试应用层工具——rio_test_dma。TSI721在处理block DMA Descriptors时,可以将Descriptors转换成以下4中rapidio操作(参考:《Tsi721 ™ User Manual》P189)rio_test_dma工具是使用的NWRITE_R。本文是在使用rio_test_dma工具进行block D

一、简介

当前使用的驱动源码来自Releases · RapidIO/kernel-rapidio · GitHub,驱动源码中包含block DMA的测试应用层工具——rio_test_dma。

TSI721在处理block DMA Descriptors时,可以将Descriptors转换成以下4中rapidio操作(参考:《Tsi721 ™ User Manual》P189)

- S-RIO NREAD

- S-RIO maintenance read

- S-RIO NWRITE/SWRITE/NWRITE_R

- S-RIO maintenance write

rio_test_dma工具是使用的NWRITE_R。

本文是在使用rio_test_dma工具进行block DMA测试的驱动流程分析笔记。

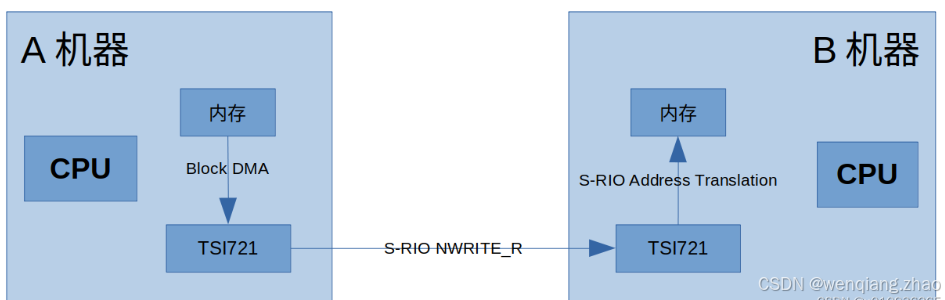

二、数据在硬件上的传输方向

在执行rio_test_dma进行数据传输时,主要涉及3个过程:

- A机器(发送端)中的 内存~TSI721;

- A机器的 TSI721 ~ B机器的 TSI721 (S-RIO NWRITE_R);

- B机器中的 TSI721~内存。

下面将对这三个过程进行分析。

三、源码执行流程

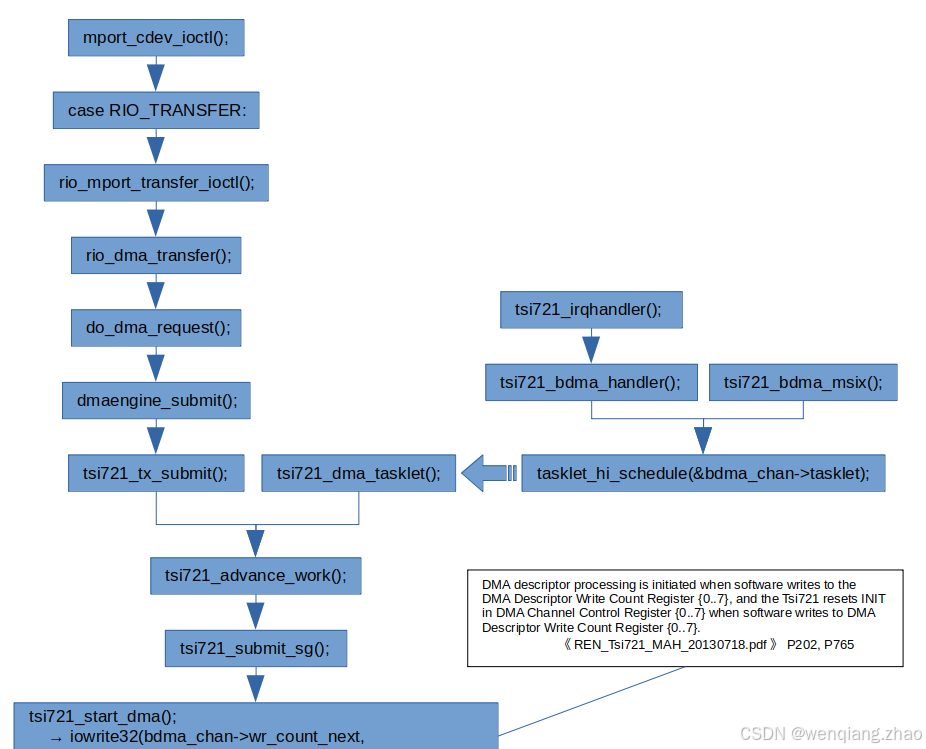

3.1 发送端 -A机器

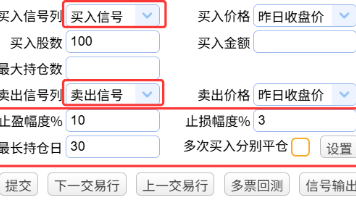

# ./rio_test_dma -M 0 -D 0x0 -A 0x2000000 -S 0x200000 -T 2 -d -v

函数栈:

3.2 A机器的 TSI721 -> B机器的 TSI721 (S-RIO NWRITE_R);

机器A 将数据传递给 机器B时,是将block DMA的数据转换成了rapidio协议里的NWRITE_R操作。这部分的工作由TSI721芯片自动完成。

NWRITE_R的具体信息请看《RapidIO ™ Interconnect Specification Part 1: Input/Output Logical Specification》(Rev. 2.1, 08/2009), PAGE 26

3.3 接收端 - B机器

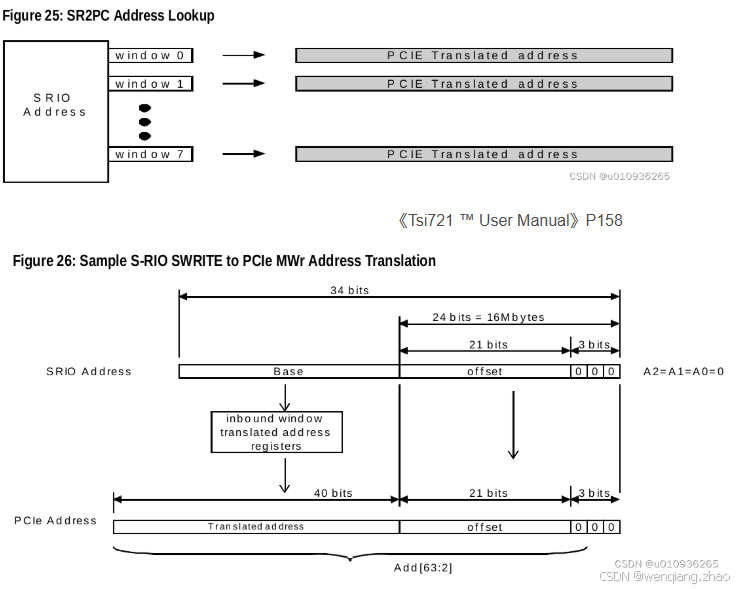

3.3.1 地址转换

此时需要把 srio 地址转换成PCIE 地址。地址转换如下:

The 34/50/66-bit address of a S-RIO request packet (NREAD, NWRITE/SWRITE/NWRITE_R) is translated using one of the

eight 66-bit inbound windows implemented in the SR2PC block.

Each window is defined by Inbound Window Translated Lower Address Register {0..7} and Inbound Window Translated

Upper Address {0..7}, and Inbound Window Size Register{0..7}

A机器通过NWRITE_R向B机器的SRIO Address写数据,经过S-RIO Address Translation后,A机器写过来的数据实际上是写到了Inbound Window Translated Lower Address Register {0..7} and Inbound Window Translated Upper Address {0..7}指定的内存中了。

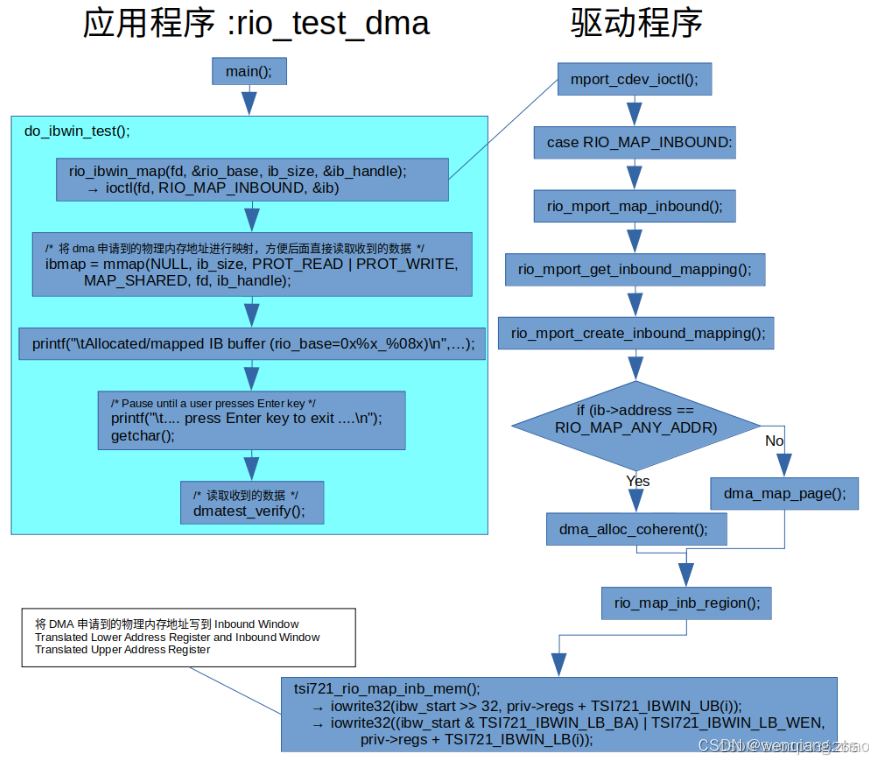

3.3.2 驱动调用关系

测试命令:# ./rio_test_dma -M 0 -I 0x1000000 -R 0x2000000 -v

上面只是把接收端的窗口映射;实际发送端和接收端代码大致一样,不一样的是接收端会被数据到来后,通过唤醒,再去读取数据。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)